| Back | << | Index | >> |

Il existe une version gratuite à l’adresse suivante :

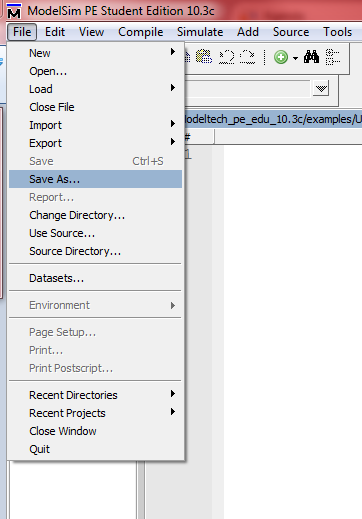

File –> New –> Source –> VHDL

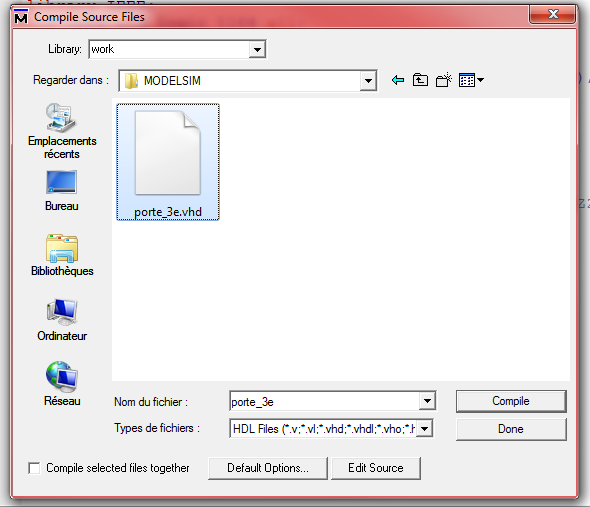

Save as : Travailler de préférence en local (compilations et tests plus rapides) dans un répertoire accessible en écriture.

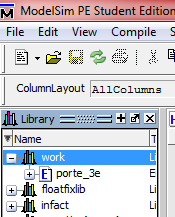

Si la compilation se fait sans erreur, Les Composants se retrouvent dans la bibliothèque work :

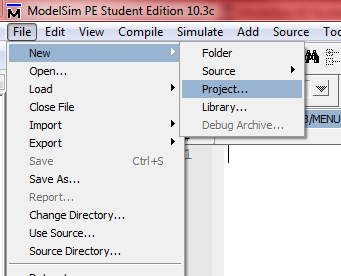

File –> New –> Project

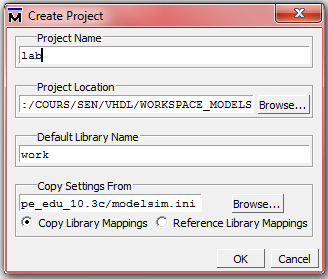

Définir un nom pour le projet et le répertoire (où se situent tous les fichiers .vhd de ce projet)

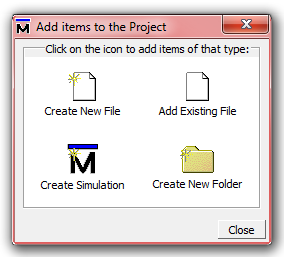

Add Existing File

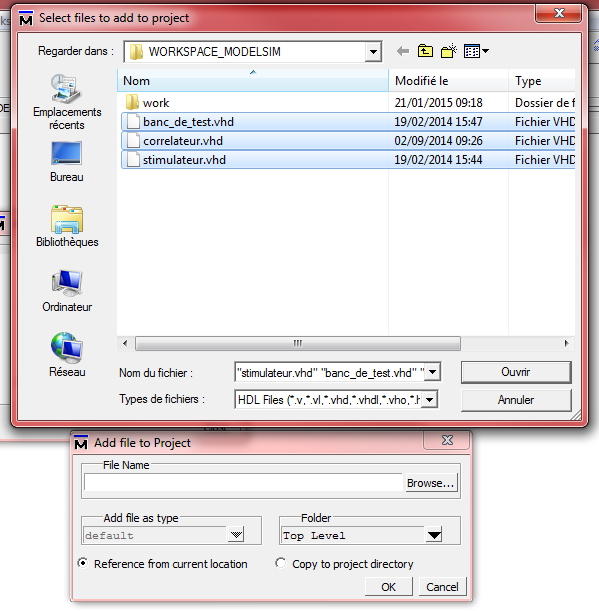

Sélectionner tous les .vhd (souris clic gauche + shift)

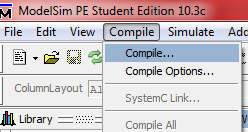

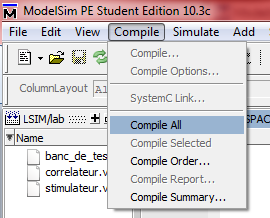

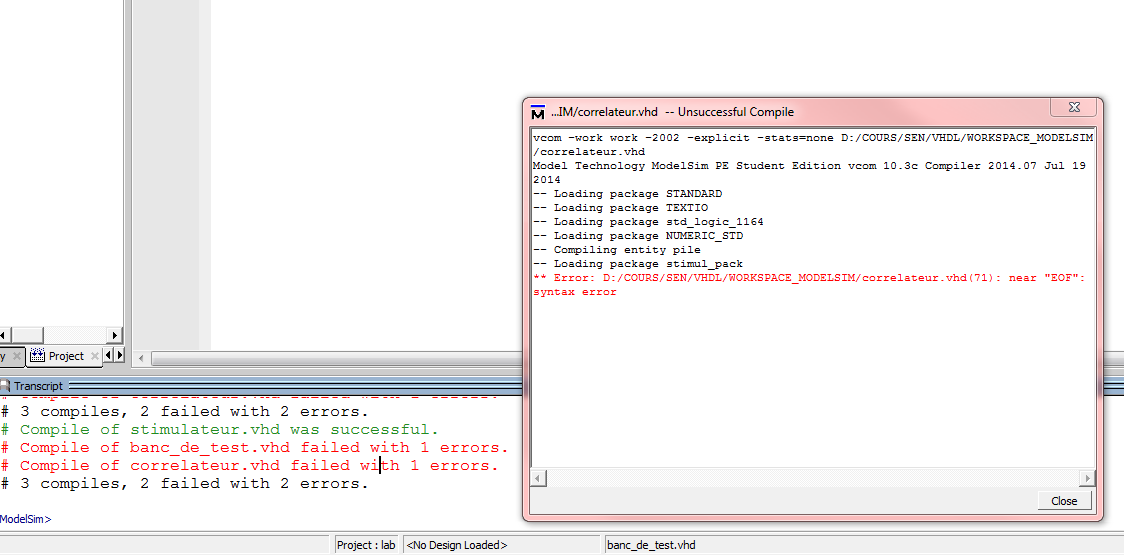

Cliquer sur les lignes en rouge de la fenêtre transcript pour avoir des informations sur les erreurs

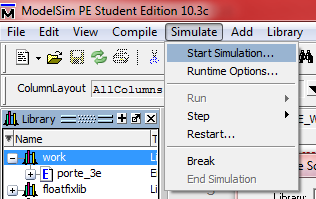

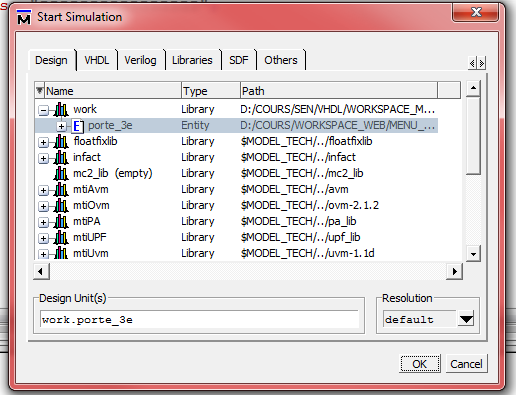

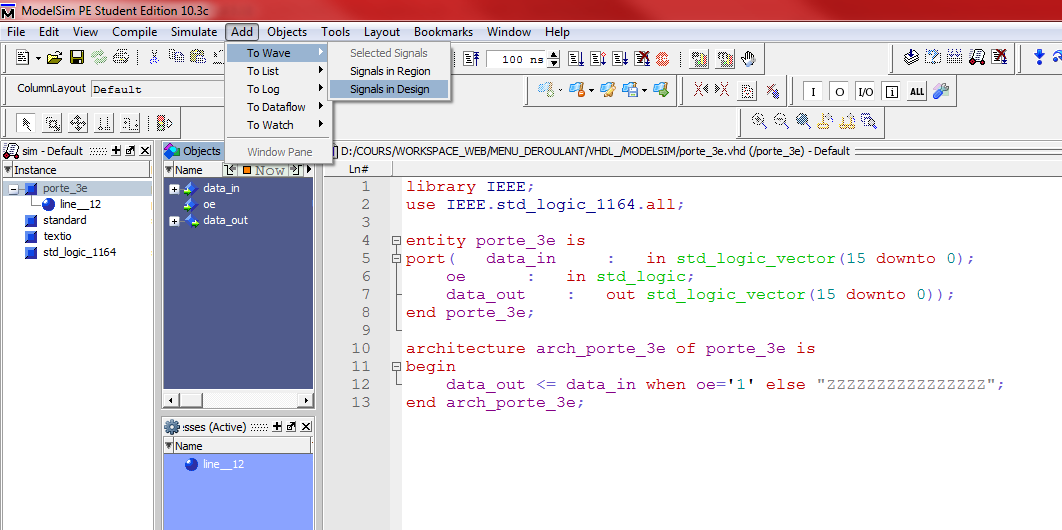

Simulate –> Start Simulation

Sélectionner le Composant à Tester

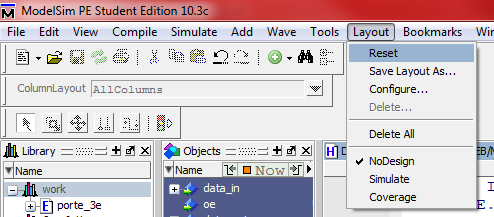

REMARQUE : Si l’agencement des fenêtre est perturbé, il est possible de retrouver la configuration initiale en faisant Layout –> reset

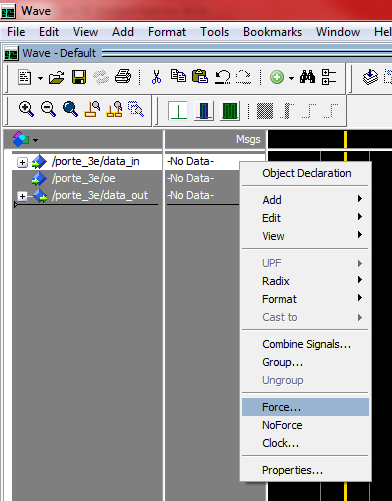

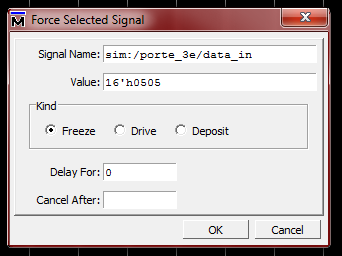

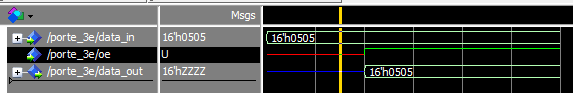

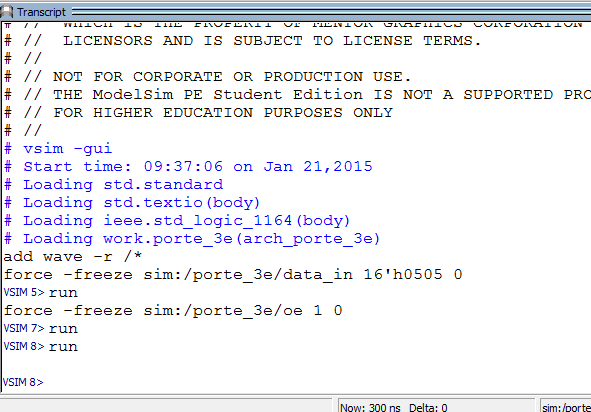

FORCAGE DES SIGNAUX : clic droit sur le signal –> force (clk s’il s’agit d’une horloge)

Bien évidemment on ne force que les entrées

REMARQUE : Pour un composant synchrone, un reset est obligatoire pour commencer

run

Réitérer les opérations Forçage / run pour vérifier le fonctionnement du composant

On peut remarquer que tout ce que nous venons de faire depuis l’ajout des signaux dans le chronogramme s’inscrit sous forme de directives dans la fenêtre transcript. On peut sauvegarder le transcript et relancer directement toutes ces directives

| Back | << | Index | >> |