| Back | << | Index | >> |

L’objectif de cet exercice est de décrire en partie un périphérique liaison série simplifié de type UART.

On considère les hypothèses simplificatrices suivantes :

Un Décodeur permet, à partir de l’adresse figurant sur le bus d’adresses, de sélectionner un registre afin de charger une donnée

présente sur le bus de données ou de forcer la valeur de ce bus.

Les registres accessibles par l’utilisateur (le microcprocesseurs) sont :

Le bit de parité est fourni par le détecteur de parité (1 pour un nombre impair de 1 dans la donnée à envoyer).

Fichier Source :

Seuls le registre sérialisateur et le séquenceur sont à compléter.

COMMENT TESTER ?

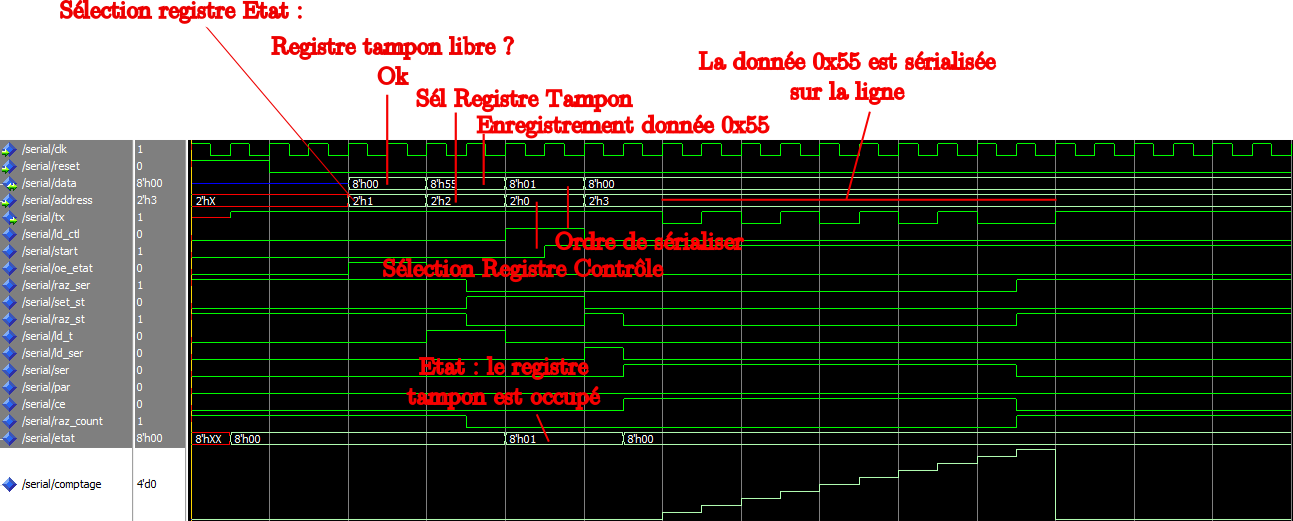

Rappelons une procédure classique pour écrire une donnée sur une liaison série :

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ce composant synchrone revient à gérer un signal interne de 11 bits (Parite / Donnée / 0 / 1)

La Sortie TX correspond au bit de poids faible de ce registre (1 à l’état de repos)

L’affectation de TX doit se faire en parallèle du process pour que TX corresponde à une copie de ce bit de poids faible.

Le chargement de la donnée et du bits de parité a lieu lorsque load=’1’.

Tant que rotate=’1’, on doit observer une rotation des bits du registre de telle sorte que chaque bit défile par la cas 0 (correspondant à TX).

La rotation peut se faire par une boucle for, ou plus simplement avec la fonction rotate_right disponible dans numeric_std

|

|

|

Proposer un diagramme d’états, et la description VHDL correspondante pour le fonctionnement suivant :

Proposer un nouveau diagramme d’états permettant de prendre en compte le chargement d’une donnée dans le tampon alors qu’une sérialisation est en cours.

|

|

|

Relier le sérialisateur au processeur mu0 (lab2) ( an ajoutant au passage un décodeur pour le bus d’adresse ) ; modifier le programme dans la mémoire de mu0 pour montrer le bon fonctionnement de l’ensemble.

| Back | << | Index | >> |