| Back | << | Index | >> |

L’objectif de cet exercice est de décrire un chronomètre simple.

Son architecture repose autour de deux compteurs, l’un pour les millisecondes, l’autre pour les secondes.

Par conséquent, TIMER_MS s’incrémente à chaque milliseconde, TIMER_S s’incrémente à chaque

seconde.

Le signal eoc est égal à 1 en fin de comptage de TIMER_MS. Ce signal permet d’autoriser le

comptage de TIMER_S.

REGISTRE_MS et REGISTRE_S permettent de sauvegarder l’état de comptage des 2 compteurs.

Le fonctionnement de l’ensemble est contôlé par le séquenceur ME_CHRONO.

L’utilisateur dispose des commandes :

La taille des compteurs et des registres est à définir de telle sorte que TIMER_MS puisse s’incrémenter jusqu’à 999, et TIMER_S jusqu’à 59.

Le chronomètre doit respecter le fonctionnement suivant :

Q1. Proposer le diagramme d’états correspondant à ce fonctionnement

Q2. Coder la machine d’état correspondante, ainsi que tous les composants constituant le chronomètre en respectant les noms des signaux proposés.

Quand on est dans l’état RUNNING ( et uniquement dans cet état ), l’appui sur rec doit actionner le

chargement des registres REGISTRE_MS et REGISTRE_S.

Attention, on ne doit enregistrer qu’une seule donnée ( au moment du passage à 1 de rec ; l’enregistrement d’une nouvelle donnée n’est possible que si

rec est repassé à 0.

Q3. Proposer une modification de la machine d’états précédente permettant d’ajouter la fonctionnalité d’enregistrement de la valeur de comptage.

Q4. Modifier l’architecture précédente afin de pouvoir compter et enregistrer les minutes.

ELEMENTS DE CORRECTION

L’objectif de cet exercice est de décrire un émetteur simplifié pour liaison série.

Le registre serialisateur reg_ser_dat contient la donnée à envoyer ( sur 8 bits ).

Ce registre est chargé lorsque le signal data_load vaut 1.

Initialement line_out vaut ‘1’ ( état de repos de la liaison, correspondant à la voie A du multiplexeur ).

Lorsque l’ordre d’envoyer la donnée est reçu ( signal serialize = ‘1’), les 4 bits du fanion doivent être envoyés, puis les 8 bits de donnée.

Q1. Proposer le diagramme d’états correspondant à ce fonctionnement

Q2. Coder la machine d’états correspondante, ainsi que tous les composants constituant l’emetteur en respectant les noms des signaux proposés.

Q3. Modifier l’architecture précédente afin de pouvoir ajouter un bit de parité ( ce bit valant ‘1’ si DATA comporte un nombre pair de ‘1’, ‘0’ sinon )

On modifie la liaison afin de pouvoir envoyer 3 données de 8 bits après le fanion.

Ces valeurs doivent être stockées dans 3 registres tampon, Le chargement de ces registres sera effectué par 3 signaux data_load1, data_load2, data_load3,

Lors de l’envoi des données, chaque registre tampon doit être transféré successivement dans le registre sérialisateur, et le bit de parité, portant sur les 3 données, doit être placé à la fin de la trame.

Q4. Proposer un schéma pour le nouveau système

Q5. Proposer le diagramme d’états correspondant à ce fonctionnement, puis coder le nouveau système

ELEMENTS DE CORRECTION

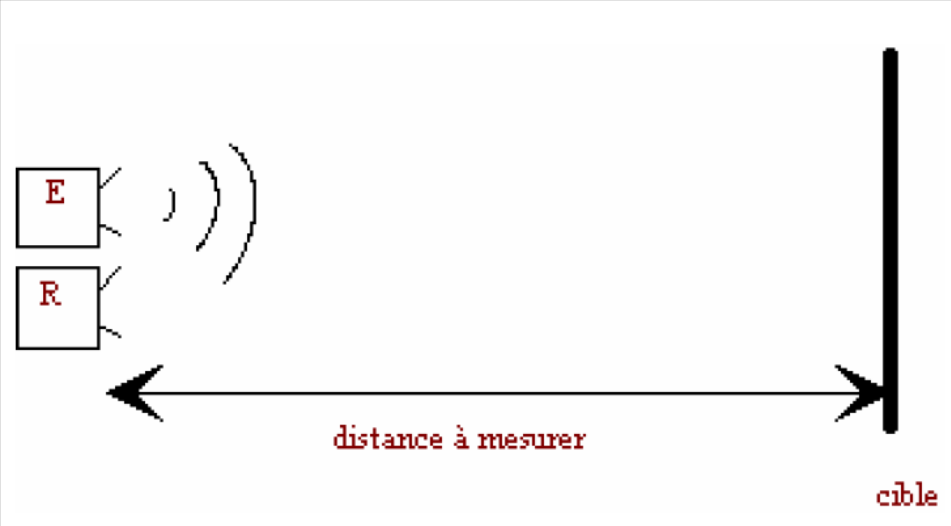

Les télémètres à ultrasons utilisent la mesure du temps de vol aller-retour d’une impulsion ultrasonore.

L’émetteur E émet périodiquement une courte impulsion ultrasonore (de l’ordre de 40 kHz),

qui se propagera dans l’air à une vitesse de l’ordre de 300 m/s,

sera réfléchie par la cible et détectée par le récepteur R.

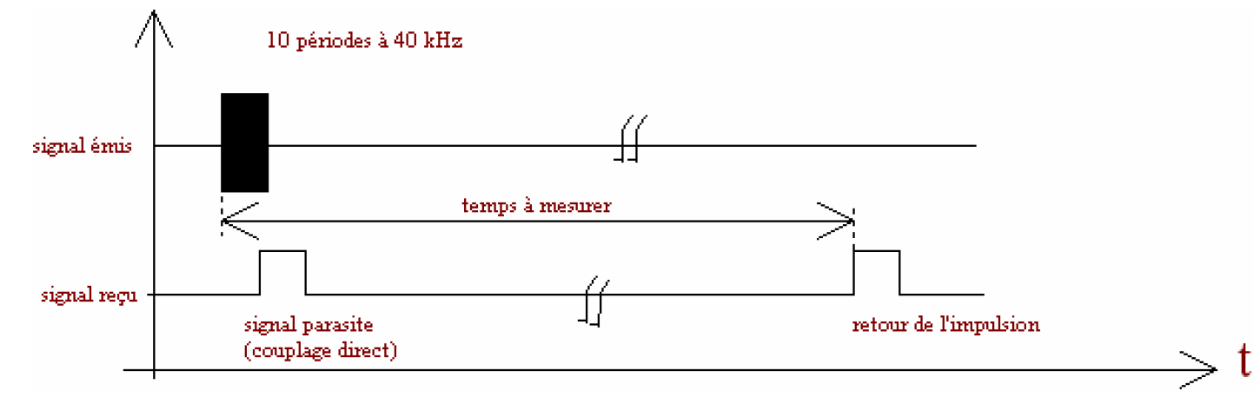

L’impulsion ultrasonore émise est constituée de 10 périodes d’une sinusoïde à 40 kHz.

Le récepteur remet en forme le signal reçu,

pour fournir un signal rectangulaire logique de même durée que l’impulsion.

Néanmoins un couplage direct entre l’émetteur et le récepteur fait apparaître un “signal reçu”

parasite peu après le début de l’émission de l’impulsion.

La chaîne de mesure associée aux transducteurs ultrasonores doit :

Le télémètre étudié ici (télémètre de poche pour le métrage de pièces de bâtiments) doit pouvoir mesurer des distances sur une plage de 0,5 à 15 m, avec une précision meilleure que le demi centimètre.

Dans tout le problème, on considère que la vitesse de propagation de l’onde ultrasonore est de 300 m/s.

L’élaboration d’un signal à la fréquence de 40 kHz est nécessaire pour générer l’onde ultrasonore.

Q1. Montrer que cette fréquence convient pour la mesure, par comptage temporel, du temps de vol, en terme de précision de mesure ( calculer pour cela la variation de temps de vol correspondant à une variation de 0.5 cm de distance, et comparer cette variation avec un comptage à 40kHz )

Q2. Donner la plage de variation du temps de vol en ms ( temps nécessaire pour mesurer les distances minimales et maximales).

Q3. En déduire la capacité minimale que doit avoir le compteur temporel fonctionnant à une fréquence de 40kHz (dans la suite on prendra 16 bits, qui correspond au format du bus de données)

La figure suivante donne l’organisation générale de la chaîne de mesure.

Le signal reset ( actif à l’état 1 ) nous place dans un état initial où tous les compteurs sont remis à zéro.

Le signal ordre_mes à 1 nous fait changer d’état afin de générer 10 périodes d’horloge sur sig_tr ( sig_tr reçoit alors clk ).

Le comptage du nombre de périodes est réalisé par compteur_emet ; en parallèle le comptage avec compteur_temps_vol est activé.

Le passage à 1 de sig_rec nous indique que le signal parasite a été reçu (ce passage à 1 peut intervenir lors de l’émission des 10 périodes de clk ) ; il faudra attendre que ce signal repasse à zéro puis à nouveau à 1 pour stopper le comptage de compteur_temps_vol.

On peut alors indiquer qu’une mesure est disponible ( data_available = 1 ), en autorisant en parallèle l’écriture de la donnée sur val_compt.

Q1. Proposer un diagramme d’états du séquenceur permettant de respecter le fonctionnement de l’émetteur-récepteur :

Q2. Réaliser la descrption VHDL du compteur, du séquenceur et de l’émetteur. Réaliser l’instanciation et démontrer le bon fonctionnement de l’ensemble à l’aide d’une simulation pertinente.

Q3. Proposer une modification de l’architecture pour fournir directement le calcul de la distance au format virgule fixe approprié.

ELEMENTS DE CORRECTION

L’objectif est d’ajouter une pile FIFO ( First In First Out ) au périphérique liaison série étudié en labo.

Cette pile peut contenir 4 données.

REMARQUE : La pile est un composant synchrone, les actions ci-dessous sont réalisées lors d’un front montant de clk.

Initialisation : La forçage à ‘1’ du signal init_FIFO entraîne l’initialisation à 0 du signal adr.

Ecriture : Le forçage à ‘1’ du signal wr_FIFO entraîne l’enregistrement de la donnée présente sur d_in dans la case fifo(adr), puis le signal adr est incrémenté de 1.

Lecture : la donnee fifo(0) est toujours présente sur d_out. Le forçage à ‘1’ du signal rd_FIFO entraine le décalage des échantillons dans la pile en écrasant le plus vieux, et la décrémentation du signal adr.

Ecriture et Lecture simultanée : le forçage à ‘1’ de wr_FIFO et rd_FIFO entraîne le décalage des échantillons de la pile et l’enregistrement de la donnée présente sur d_in dans la case fifo(adr-1). La valeur de adr n’est pas modifiée

REMARQUE :

Q1. Proposer une description VHDL de la pile FIFO, et valider son bon fonctionnement avec une simulation pertiente ( Faire valider cette simulation par l’enseignant ).

REMARQUES :

Le décalage des échantillons nécessite l’utilisation d’une boucle for :

for i in ... to ... loop

...

end loop;

Après un état d’initialisation de l’ensemble des composants synchrones, le signal ld_FIFO à ‘1’ amène dans un état où les données présentes sur le bus DATA sont enregistrées à chaque coup d’horloge dans la pile.

Lorsque la pile est pleine, le registre d’état doit être forcé à 1, indiquant au processeur qu’il ne faut rien écrire d’autre dans la pile.

Si le signal start vaut ‘1’, il faut :

REMARQUE : Dès lors que la pile n’est plus pleine, le registre d’état doit être forcé à 0.

Q2. Proposer un diagramme d’états permettant de décrire le fonctionnement du composant sequenceur_serial.

Q3. Proposer une description VHDL du séquenceur, puis compléter l’instanciation des composants afin d’intégrer la pile FIFO dans le système. Réaliser une simulation pertiente pour faire valider le bon fonctionnement de l’ensemble.

Q4. Proposer une modification du diagramme d’états précédent afin de gérer la mise à jour du registre d’état au cours de la sérialisation, et valider par une simulation ce nouveau fonctionnement.

ELEMENTS DE CORRECTION

| Back | << | Index | >> |